- 您现在的位置:买卖IC网 > Sheet目录345 > MT42L256M32D4KP-3 IT:A (Micron Technology Inc)IC LPDDR2 SDRAM 8GBIT 168FBGA

�� �

�

�

�2Gb:� x16,� x32� Mobile� LPDDR2� SDRAM� S4�

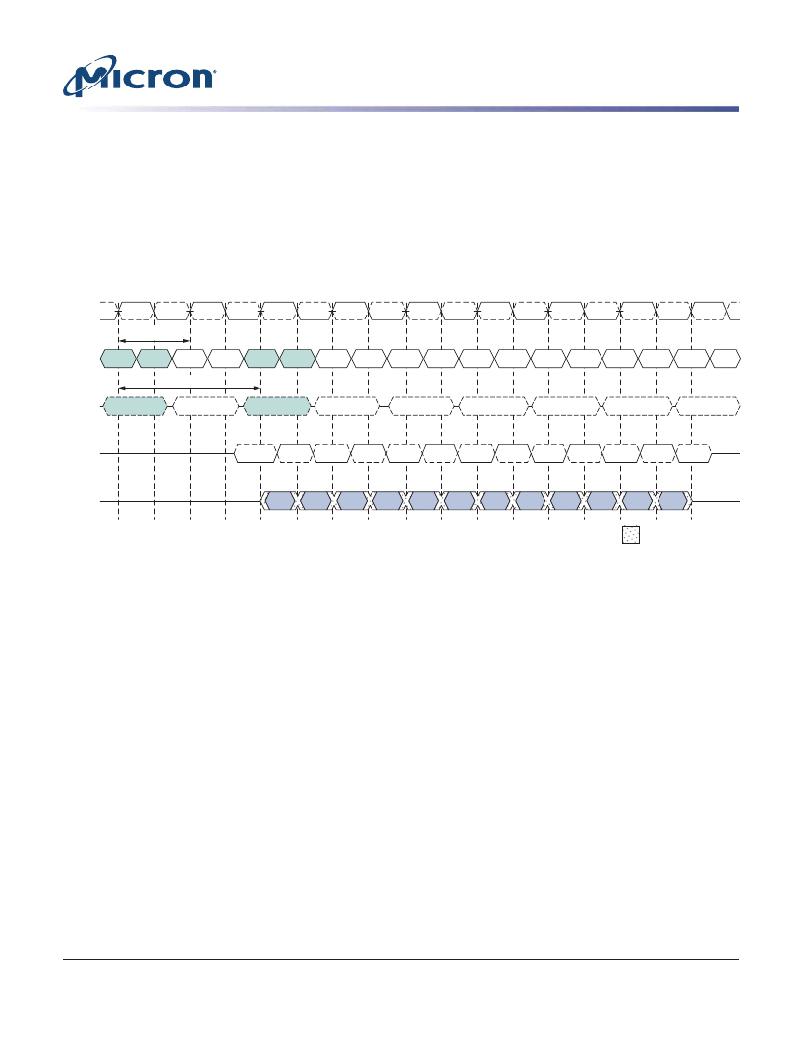

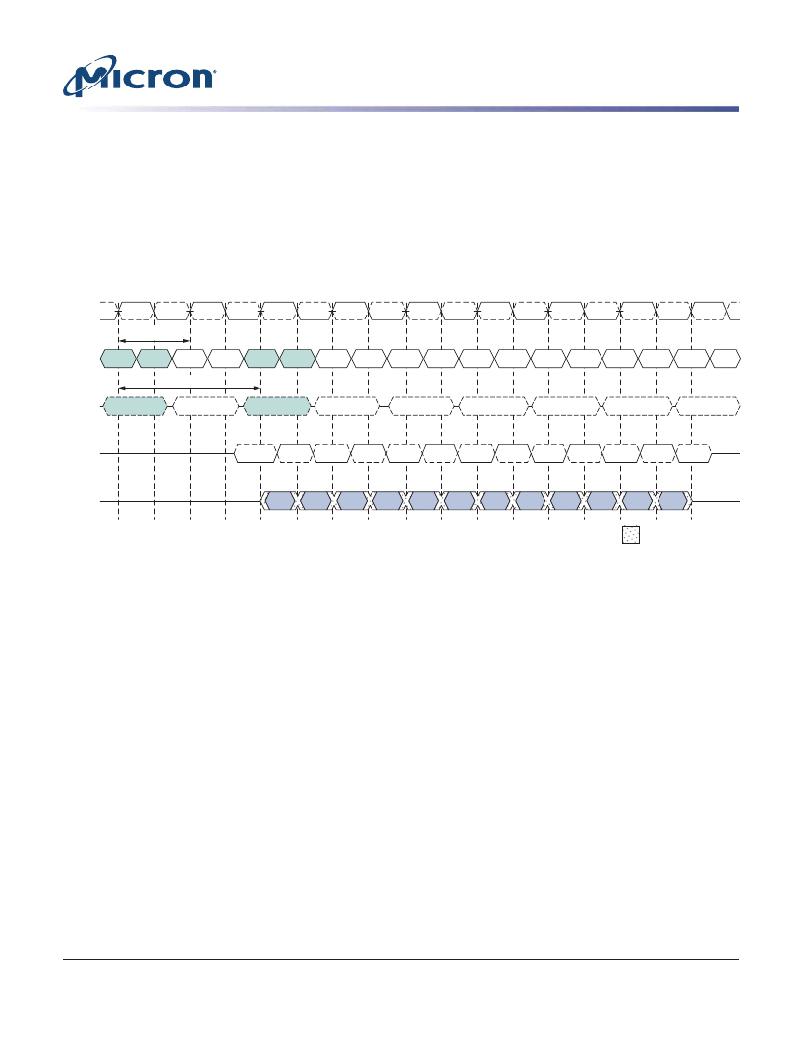

�BURST� TERMINATE� Command�

�WRITEs� Interrupted� by� a� WRITE�

�A� burst� WRITE� can� only� be� interrupted� by� another� WRITE� with� a� 4-bit� burst� boundary,�

�provided� that� t� CCD� (MIN)� is� met.�

�A� WRITE� burst� interrupt� can� occur� on� even� clock� cycles� after� the� initial� WRITE� com-�

�mand,� provided� that� t� CCD� (MIN)� is� met.�

�Figure� 43:� WRITE� Burst� Interrupt� Timing� –� WL� =� 1,� BL� =� 8,� t� CCD� =� 2�

�T0�

�T1�

�T2�

�T3�

�T4�

�T5�

�T6�

�T7�

�T8�

�CK#�

�CK�

�WL� =� 1�

�CA[9:0]�

�Bank� m�

�col� addr� a�

�Col� addr� a�

�Bank� n�

�col� addr� b�

�Col� addr� b�

�t� CCD�

�=2�

�CMD�

�WRITE�

�NOP�

�WRITE�

�NOP�

�NOP�

�NOP�

�NOP�

�NOP�

�NOP�

�DQS#�

�DQS�

�DQ�

�D� IN� A0�

�D� IN� A1�

�D� IN� A2�

�D� IN� A3�

�D� IN� B0�

�D� IN� B1�

�D� IN� B2�

�D� IN� B3�

�D� IN� B4�

�D� IN� B5�

�D� IN� B6�

�D� IN� B7�

�Transitioning� data�

�Notes:�

�1.� WRITEs� can� only� be� interrupted� by� other� WRITEs� or� the� BST� command.�

�2.� The� effective� burst� length� of� the� first� WRITE� equals� two� times� the� number� of� clock� cycles�

�between� the� first� WRITE� and� the� interrupting� WRITE.�

�BURST� TERMINATE� Command�

�The� BURST� TERMINATE� (BST)� command� is� initiated� with� CS#� LOW,� CA0� HIGH,� CA1�

�HIGH,� CA2� LOW,� and� CA3� LOW� at� the� rising� edge� of� the� clock.� A� BST� command� can� only�

�be� issued� to� terminate� an� active� READ� or� WRITE� burst.� Therefore,� a� BST� command� can�

�only� be� issued� up� to� and� including� BL/2� -� 1� clock� cycles� after� a� READ� or� WRITE� com-�

�mand.� The� effective� burst� length� of� a� READ� or� WRITE� command� truncated� by� a� BST�

�command� is� as� follows:�

�?� Effective� burst� length� =� 2� � (number� of� clock� cycles� from� the� READ� or� WRITE� com-�

�mand� to� the� BST� command).�

�?� If� a� READ� or� WRITE� burst� is� truncated� with� a� BST� command,� the� effective� burst� length�

�of� the� truncated� burst� should� be� used� for� BL� when� calculating� the� minimum� READ-�

�to-WRITE� or� WRITE-to-READ� delay.�

�?� The� BST� command� only� affects� the� most� recent� READ� or� WRITE� command.� The� BST�

�command� truncates� an� ongoing� READ� burst� RL� � t� CK� +� t� DQSCK� +� t� DQSQ� after� the� ris-�

�ing� edge� of� the� clock� where� the� BST� command� is� issued.� The� BST� command� truncates�

�an� ongoing� WRITE� burst� WL� � t� CK� +� t� DQSS� after� the� rising� edge� of� the� clock� where� the�

�BST� command� is� issued.�

�PDF:� 09005aef83f3f2eb�

�2gb_mobile_lpddr2_s4_g69a.pdf� –� Rev.� N� 3/12� EN�

�65�

�Micron� Technology,� Inc.� reserves� the� right� to� change� products� or� specifications� without� notice.�

�2010� Micron� Technology,� Inc.� All� rights� reserved.�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MT45W1MW16BDGB-708 AT

IC PSRAM 16MBIT 104MHZ 54VFBGA

MT48H32M16LFB4-75B IT:C

IC SDRAM 512MB 54VFBGA

MT48H8M16LFB4-75 IT:K TR

IC SDRAM 128MBIT 133MHZ 54VFBGA

MTC100-JA2-P34

CONTACT INSERT PIN

MX841BE

IC CONVERTER WHITE LED 8-SOIC

MXHV9910BTR

IC LED DRIVER HIGH BRIGHT 8-SOIC

MXN12FB12F

MOTOR BRUSHED DC 12V 2922RPM

MXN13FB08B1

MOTOR BRUSHED DC 8V 4714RPM

相关代理商/技术参数

MT42L256M32D4KP-MS

制造商:Micron Technology Inc 功能描述:256MX32 LPDDR2 PLASTIC IND TEMP GREEN WFBGA 1.2V - Bulk